### 32-Bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ 5V Microcontroller

# HT32F50020/HT32F50030 User Manual

Revision: V1.00 Date: February 08, 2023

www.holtek.com

# **Table of Contents**

| 1 | Introduction                                                                                     | . 16 |

|---|--------------------------------------------------------------------------------------------------|------|

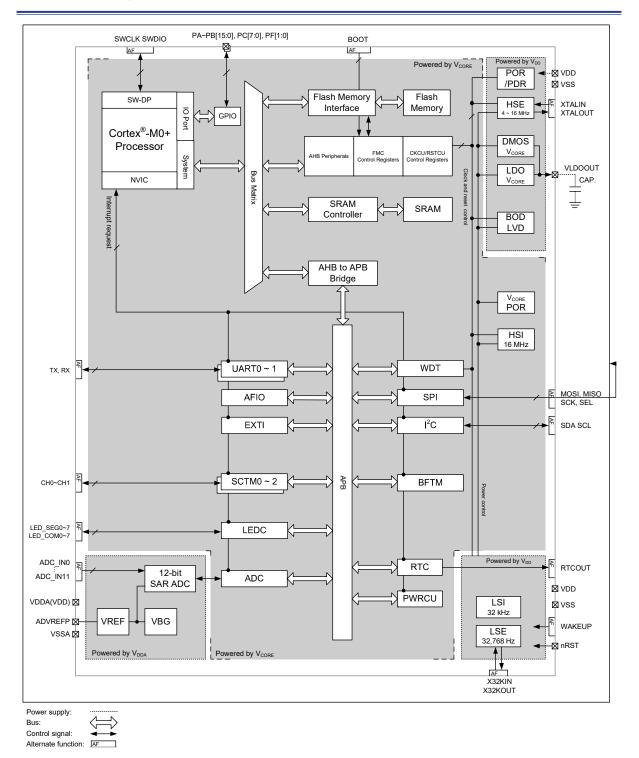

|   | Overview                                                                                         | . 16 |

|   | Features                                                                                         | . 16 |

|   | Device Information                                                                               | . 19 |

|   | Block Diagram                                                                                    | . 20 |

| 2 | Document Conventions                                                                             | . 21 |

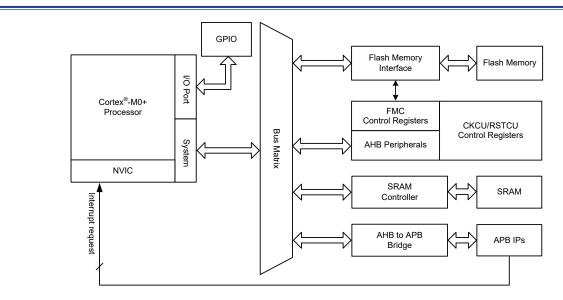

| 3 | System Architecture                                                                              | . 22 |

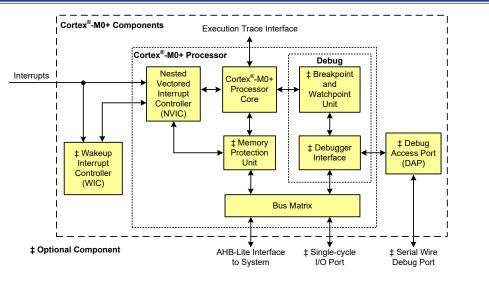

|   | Arm <sup>®</sup> Cortex <sup>®</sup> -M0+ Processor                                              | . 22 |

|   | Bus Architecture                                                                                 | . 23 |

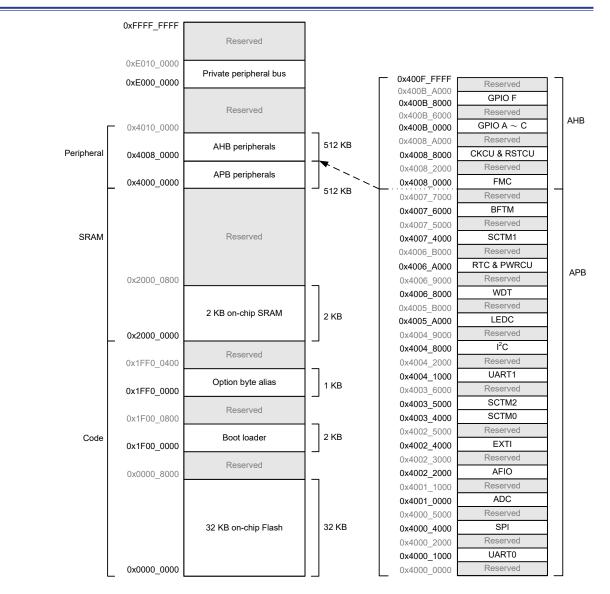

|   | Memory Organization                                                                              |      |

|   | Метогу Мар                                                                                       |      |

|   | Embedded Flash Memory                                                                            |      |

|   | Embedded SRAM Memory                                                                             | . 26 |

|   | AHB Peripherals                                                                                  | . 26 |

|   | APB Peripherals                                                                                  | . 26 |

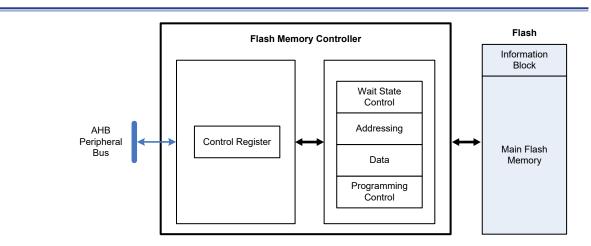

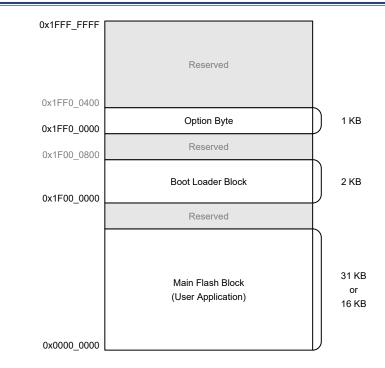

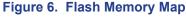

| 4 | Flash Memory Controller (FMC)                                                                    | 27   |

| 1 | Introduction                                                                                     |      |

|   | Features                                                                                         |      |

|   | Functional Descriptions                                                                          |      |

|   | Flash Memory Map                                                                                 |      |

|   | Flash Memory Architecture                                                                        |      |

|   | Booting Configuration                                                                            |      |

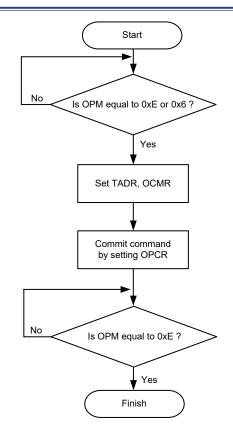

|   | Page Erase                                                                                       |      |

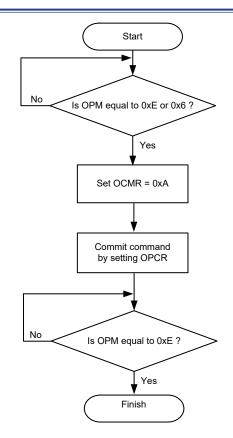

|   | Mass Erase                                                                                       |      |

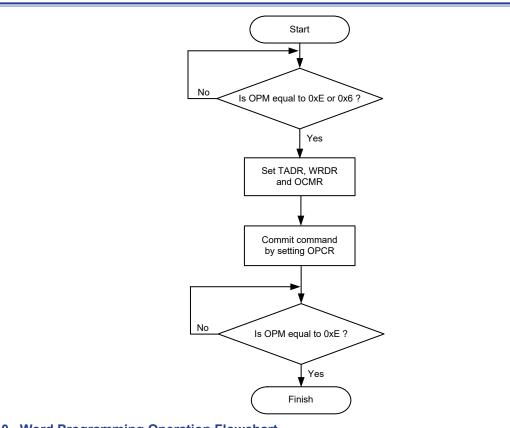

|   | Word Programming                                                                                 | . 32 |

|   | Option Byte Description                                                                          | . 33 |

|   | Page Erase/Program Protection                                                                    | . 34 |

|   | Security Protection                                                                              | . 35 |

|   | Register Map                                                                                     | . 36 |

|   | Register Descriptions                                                                            | . 37 |

|   | Flash Target Address Register – TADR                                                             | . 37 |

|   | Flash Write Data Register – WRDR                                                                 |      |

|   | Flash Operation Command Register – OCMR                                                          |      |

|   | Flash Operation Control Register – OPCR                                                          |      |

|   | Flash Operation Interrupt Enable Register – OIER                                                 |      |

|   | Flash Operation Interrupt and Status Register – OISR                                             |      |

|   | Flash Page Erase/Program Protection Status Register – PPSR                                       |      |

|   | Flash Security Protection Status Register – CPSR<br>Flash Vector Mapping Control Register – VMCR |      |

|   | Flash vector Mapping Control Register - VMCR                                                     | 40   |

|   | Flash Manufacturer and Device ID Register – MDID                    |    |

|---|---------------------------------------------------------------------|----|

|   | Flash Page Number Status Register – PNSR                            |    |

|   | Flash Page Size Status Register – PSSR                              |    |

|   | Device ID Register – DIDR                                           |    |

|   | Custom ID Register n – CIDRn (n = 0 ~ 3)                            | 50 |

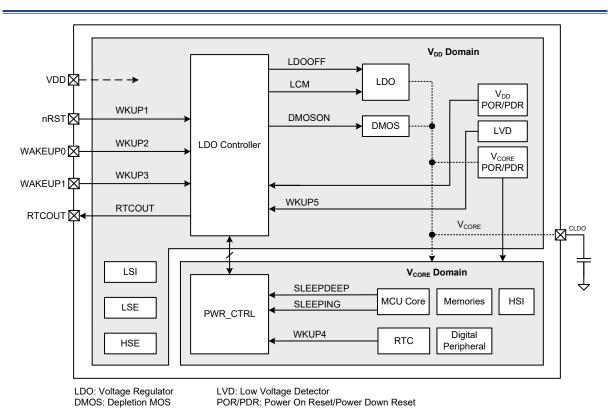

| 5 | Power Control Unit (PWRCU)                                          | 51 |

|   | Introduction                                                        | 51 |

|   | Features                                                            |    |

|   | Functional Descriptions                                             |    |

|   | $V_{DD}$ Power Domain                                               |    |

|   | V <sub>CORE</sub> Power Domain                                      |    |

|   | Operation Modes                                                     |    |

|   | Register Map                                                        |    |

|   |                                                                     |    |

|   | Register Descriptions                                               |    |

|   | Power Control Status Register – PWRSR                               |    |

|   | Power Control Register – PWRCR                                      |    |

|   | Low Voltage / Brown Out Detect Control and Status Register – LVDCSR |    |

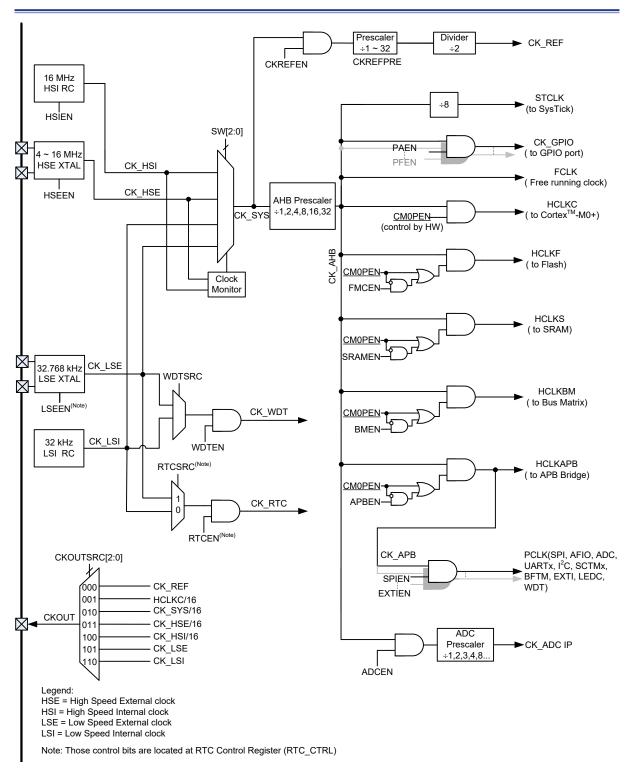

| 6 | Clock Control Unit (CKCU)                                           |    |

|   | Introduction                                                        | 62 |

|   | Features                                                            | 64 |

|   | Functional Descriptions                                             | 64 |

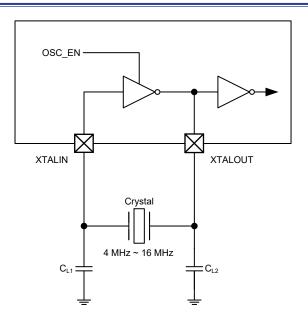

|   | High Speed External Crystal Oscillator – HSE                        | 64 |

|   | High Speed Internal RC Oscillator – HSI                             | 65 |

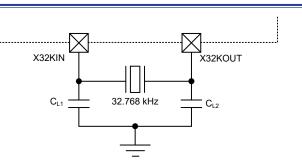

|   | Low Speed External Crystal Oscillator – LSE                         | 65 |

|   | Low Speed Internal RC Oscillator – LSI                              |    |

|   | Clock Ready Flag                                                    |    |

|   | System Clock (CK_SYS) Selection                                     | 66 |

|   | HSE Clock Monitor                                                   | 67 |

|   | Clock Output Capability                                             | 67 |

|   | Register Map                                                        | 67 |

|   | Register Descriptions                                               | 68 |

|   | Global Clock Configuration Register – GCFGR                         | 68 |

|   | Global Clock Control Register – GCCR                                | 69 |

|   | Global Clock Status Register – GCSR                                 | 70 |

|   | Global Clock Interrupt Register – GCIR                              | 71 |

|   | AHB Configuration Register – AHBCFGR                                | 72 |

|   | AHB Clock Control Register – AHBCCR                                 | 73 |

|   | APB Configuration Register – APBCFGR                                | 74 |

|   | APB Clock Control Register 0 – APBCCR0                              | 75 |

|   | APB Clock Control Register 1 – APBCCR1                              | 76 |

|   | Clock Source Status Register – CKST                                 |    |

|   | MCU Debug Control Register – MCUDBGCR                               |    |

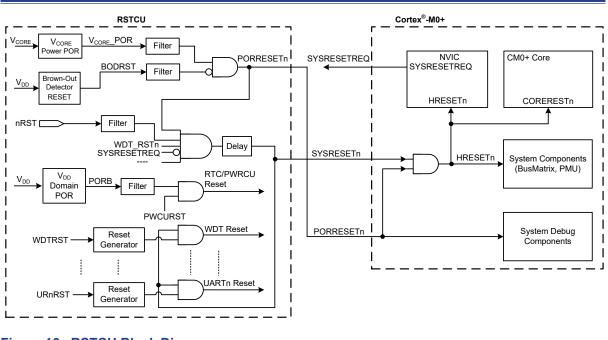

|     | Reset Control Unit (RSTCU)                               |      |

|-----|----------------------------------------------------------|------|

| I   | ntroduction                                              | .80  |

| F   | Functional Descriptions                                  | .80  |

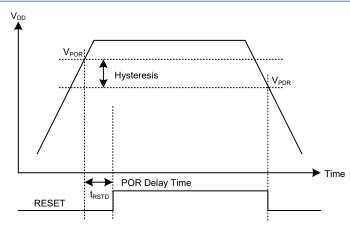

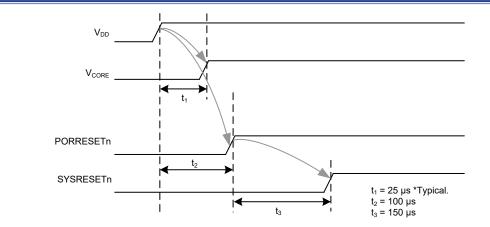

|     | Power-On Reset                                           | . 80 |

|     | System Reset                                             |      |

|     | AHB and APB Unit Reset                                   | . 81 |

| F   | Register Map                                             | .81  |

| F   | Register Descriptions                                    | .82  |

|     | Global Reset Status Register – GRSR                      |      |

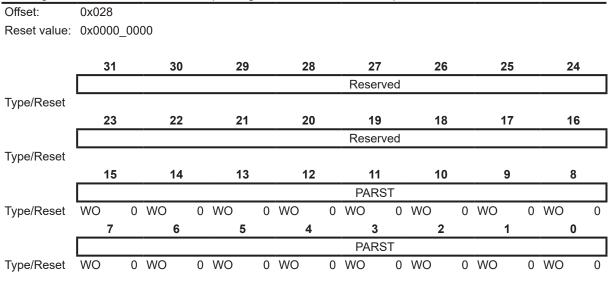

|     | AHB Peripheral Reset Register – AHBPRSTR                 |      |

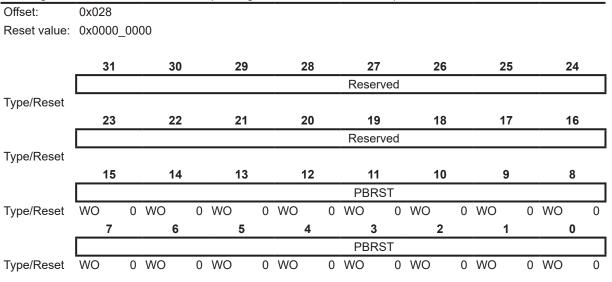

|     | APB Peripheral Reset Register 0 – APBPRSTR0              | . 84 |

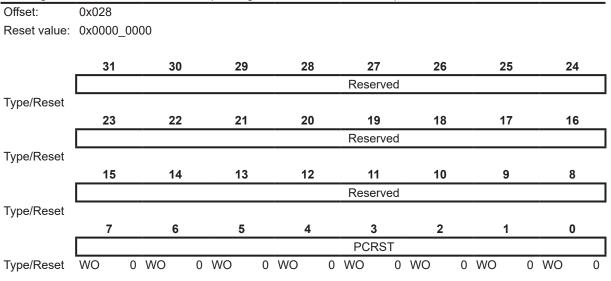

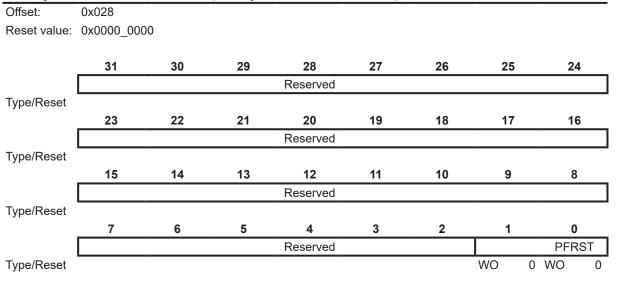

|     | APB Peripheral Reset Register 1 – APBPRSTR1              | . 85 |

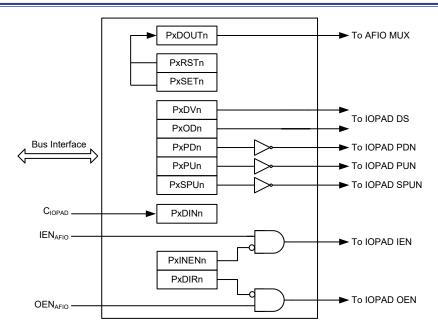

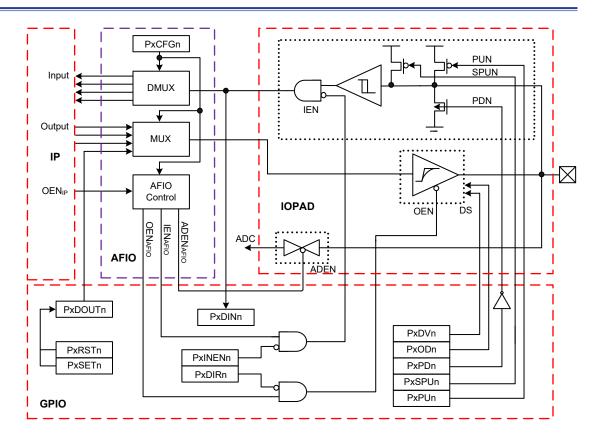

| 8 ( | General Purpose I/O (GPIO)                               | 86   |

|     | ntroduction                                              |      |

|     |                                                          |      |

|     | Features                                                 |      |

| F   | Functional Descriptions                                  |      |

|     | Default GPIO Pin Configuration                           |      |

|     | General Purpose I/O – GPIO                               |      |

|     | GPIO Locking Mechanism                                   | . 89 |

| F   | Register Map                                             | .89  |

| F   | Register Descriptions                                    | .91  |

|     | Port A Data Direction Control Register – PADIRCR         | . 91 |

|     | Port A Input Function Enable Control Register – PAINER   | . 92 |

|     | Port A Pull-Up Selection Register – PAPUR                | . 93 |

|     | Port A Pull-Down Selection Register – PAPDR              | . 94 |

|     | Port A Open-Drain Selection Register – PAODR             | . 95 |

|     | Port A Drive Current Selection Register – PADRVR         | . 96 |

|     | Port A Lock Register – PALOCKR                           | . 97 |

|     | Port A Data Input Register – PADINR                      | . 98 |

|     | Port A Output Data Register – PADOUTR                    |      |

|     | Port A Output Set/Reset Control Register – PASRR         | . 99 |

|     | Port A Output Reset Register – PARR                      |      |

|     | Port A Sink Current Enhanced Selection Register – PASCER |      |

|     | Port B Data Direction Control Register – PBDIRCR         |      |

|     | Port B Input Function Enable Control Register – PBINER   |      |

|     | Port B Pull-Up Selection Register – PBPUR                |      |

|     | Port B Pull-Down Selection Register – PBPDR              |      |

|     | Port B Open-Drain Selection Register – PBODR             |      |

|     | Port B Drive Current Selection Register – PBDRVR         |      |

|     | Port B Lock Register – PBLOCKR                           |      |

|     | Port B Data Input Register – PBDINR                      |      |

|     | Port B Output Data Register – PBDOUTR                    |      |

|     | Port B Output Set/Reset Control Register – PBSRR         | 109  |

|    | Port B Output Reset Register – PBRR                           |     |

|----|---------------------------------------------------------------|-----|

|    | Port B Sink Current Enhanced Selection Register – PBSCER      | 110 |

|    | Port C Data Direction Control Register – PCDIRCR              | 111 |

|    | Port C Input Function Enable Control Register – PCINER        | 112 |

|    | Port C Pull-Up Selection Register – PCPUR                     | 113 |

|    | Port C Pull-Down Selection Register – PCPDR                   | 114 |

|    | Port C Open-Drain Selection Register – PCODR                  | 115 |

|    | Port C Drive Current Selection Register – PCDRVR              | 116 |

|    | Port C Lock Register – PCLOCKR                                | 117 |

|    | Port C Data Input Register – PCDINR                           | 118 |

|    | Port C Output Data Register – PCDOUTR                         | 118 |

|    | Port C Output Set/Reset Control Register – PCSRR              | 119 |

|    | Port C Output Reset Register – PCRR                           | 120 |

|    | Port C Sink Current Enhanced Selection Register – PCSCER      | 120 |

|    | Port F Data Direction Control Register – PFDIRCR              | 121 |

|    | Port F Input Function Enable Control Register – PFINER        | 122 |

|    | Port F Pull-Up Selection Register – PFPUR                     | 123 |

|    | Port F Pull-Down Selection Register – PFPDR                   | 124 |

|    | Port F Open-Drain Selection Register – PFODR                  | 125 |

|    | Port F Drive Current Selection Register – PFDRVR              | 126 |

|    | Port F Lock Register – PFLOCKR                                | 127 |

|    | Port F Data Input Register – PFDINR                           | 128 |

|    | Port F Output Data Register – PFDOUTR                         | 128 |

|    | Port F Sink Current Enhanced Selection Register – PFSCER      | 129 |

|    | Port F Output Set/Reset Control Register – PFSRR              | 130 |

|    | Port F Output Reset Register – PFRR                           | 131 |

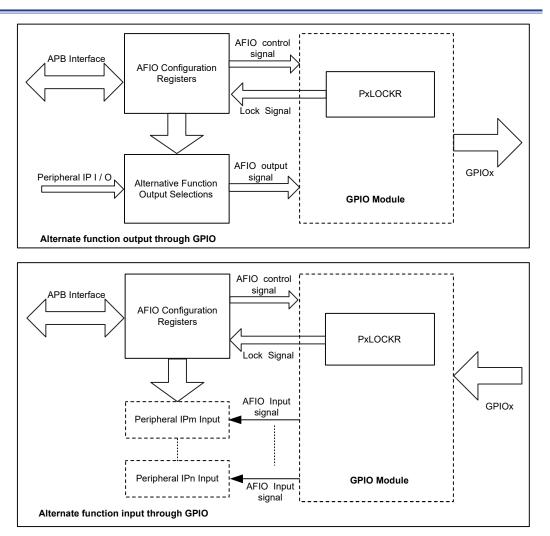

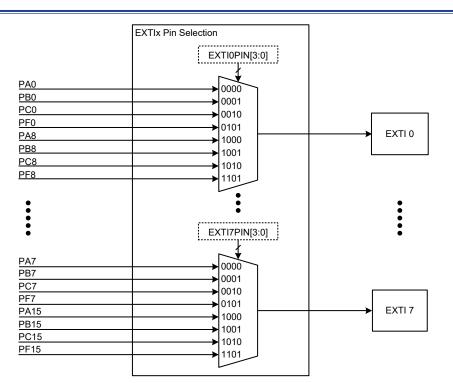

| 0  | Alternate Function Input / Output Control Unit (AFIO)         | 420 |

| 9  |                                                               |     |

|    | Introduction                                                  |     |

|    | Features                                                      | 133 |

|    | Functional Descriptions                                       | 133 |

|    | External Interrupt Pin Selection                              | 133 |

|    | Alternate Function                                            |     |

|    | Lock Mechanism                                                |     |

|    | Register Map                                                  | 134 |

|    | Register Descriptions                                         |     |

|    | EXTI Source Selection Register – ESSR                         |     |

|    | GPIO x Configuration Low Register – GPxCFGLR, x = A, B, C, F  |     |

|    | GPIO x Configuration High Register – GPxCFGHR, x = A, B, C, F |     |

|    |                                                               |     |

| 1( | 0 Nested Vectored Interrupt Controller (NVIC)                 |     |

|    | Introduction                                                  | 138 |

|    | Features                                                      |     |

|    |                                                               |     |

| Functional Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysTick Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

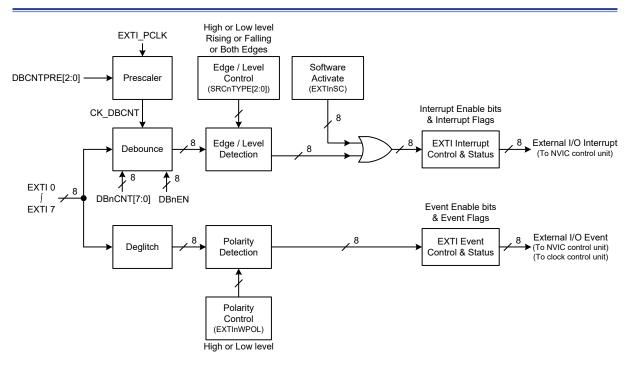

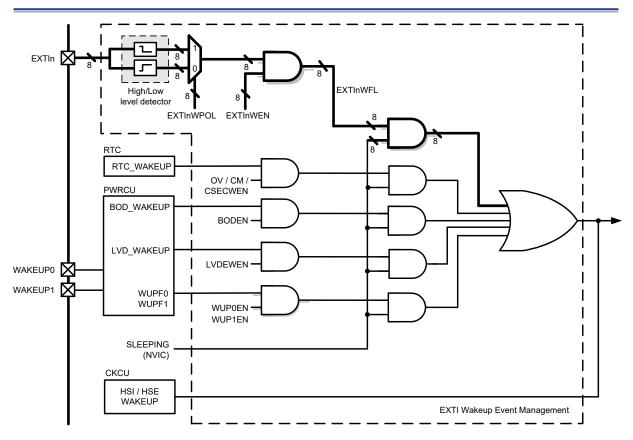

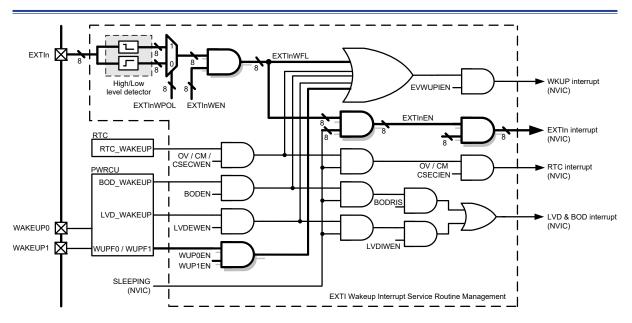

| 11 External Interrupt / Event Controller (EXTI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| Functional Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| Wakeup Event Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| External Interrupt/Event Line Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

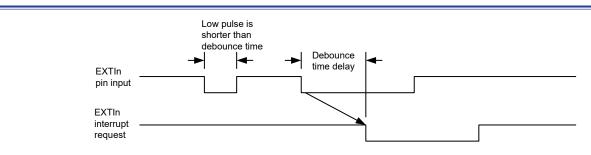

| Interrupt and Debounce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                      |

| EXTI Interrupt n Configuration Register – EXTICFGRn, n = 0 ~ 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| EXTI Interrupt Control Register – EXTICR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| EXTI Interrupt Edge Flag Register – EXTIEDGEFLGR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

| EXTI Interrupt Edge Status Register – EXTIEDGESR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

| EXTI Interrupt Software Set Command Register – EXTISSCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| EXTI Interrupt Wakeup Control Register – EXTIWAKUPCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

| EXTI Interrupt Wakeup Polarity Register – EXTIWAKUPPOLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| EXTI Interrupt Wakeup Flag Register – EXTIWAKUPFLG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 151                                                                                                                                                                  |

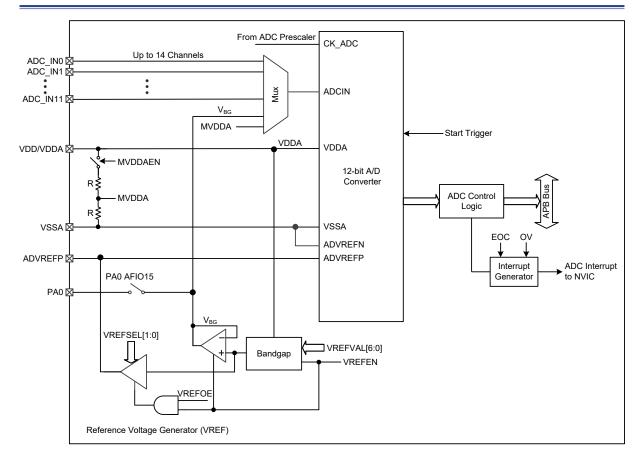

| 12 Analog to Digital Converter (ADC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

| 12 Analog to Digital Converter (ADC)<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

| 12 Analog to Digital Converter (ADC)<br>Introduction<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 151                                                                                                                                                                  |

| Introduction<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

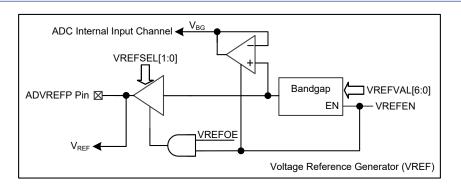

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator<br>V <sub>DDA</sub> Voltage Monitor                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator                                                                                                                                                                                                                                                                                                                                                                                | 151<br>151<br>152<br>152<br>152<br>152<br>152<br>154<br>154<br>154<br>154<br>154<br>154<br>155<br>155<br>155<br>156<br>156                                           |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator                                                                                                                                                                                                                                                                                                                                                                                | 151<br>151<br>152<br>152<br>152<br>152<br>152<br>154<br>154<br>154<br>154<br>154<br>155<br>155<br>155<br>156<br>156<br>156<br>158                                    |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator<br>V <sub>DDA</sub> Voltage Monitor<br>Register Map<br>Register Descriptions<br>ADC Conversion Control Register – ADCCR<br>ADC Conversion List Register – ADCLST<br>ADC Input Sampling Time Register – ADCSTR                                                                                                                                                                                                          |                                                                                                                                                                      |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator<br>Vodtage Reference Generator<br>Vodtage Reference Generator<br>Vodtage Reference Generator<br>Vodtage Reference Generator<br>Vodtage Monitor<br>Register Map<br>Register Descriptions<br>ADC Conversion Control Register – ADCCR<br>ADC Conversion List Register – ADCLST<br>ADC Input Sampling Time Register – ADCSTR<br>ADC Conversion Data Register y – ADCDRy, y = 0 ~ 3 | 151<br>151<br>152<br>152<br>152<br>152<br>152<br>154<br>154<br>154<br>154<br>154<br>154<br>155<br>155<br>155<br>156<br>156<br>156<br>156<br>158<br>159<br>160        |

| Introduction<br>Features<br>Functional Descriptions<br>ADC Clock Setup<br>Channel Selection<br>Conversion Mode<br>Start Conversion by Software Trigger<br>Sampling Time Setting<br>Data Format<br>Interrupts<br>Voltage Reference Generator<br>V <sub>DDA</sub> Voltage Monitor<br>Register Map<br>Register Descriptions<br>ADC Conversion Control Register – ADCCR<br>ADC Conversion List Register – ADCLST<br>ADC Input Sampling Time Register – ADCSTR                                                                                                                                                                                                          | 151<br>151<br>152<br>152<br>152<br>152<br>152<br>154<br>154<br>154<br>154<br>154<br>155<br>155<br>155<br>155<br>156<br>156<br>156<br>158<br>158<br>159<br>160<br>161 |

| ADC Interrupt Status Register – ADCISR            |     |

|---------------------------------------------------|-----|

| ADC Interrupt Clear Register – ADCICLR            |     |

| Voltage Reference Control Register – VREFCR       |     |

| Voltage Reference Value Register – VREFVALR       |     |

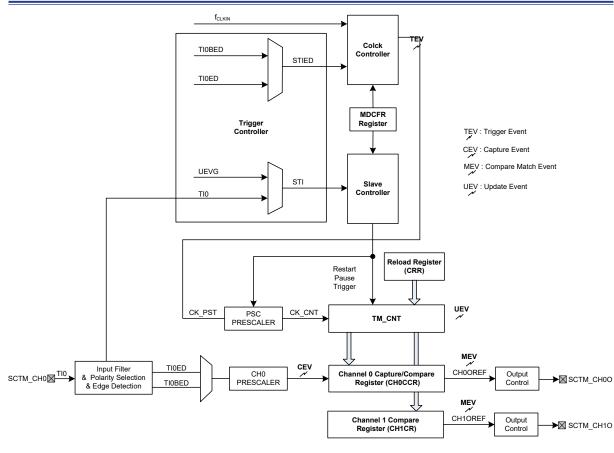

| 13 Single-Channel Timer (SCTM)                    |     |

| Introduction                                      |     |

| Features                                          | 169 |

| Functional Descriptions                           |     |

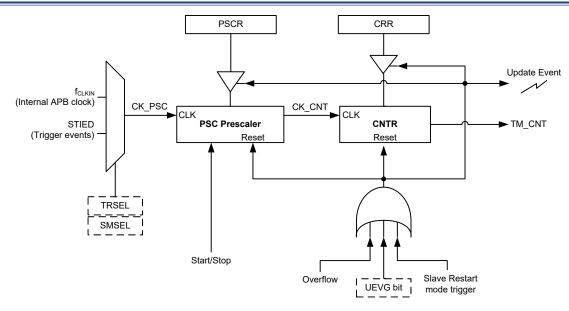

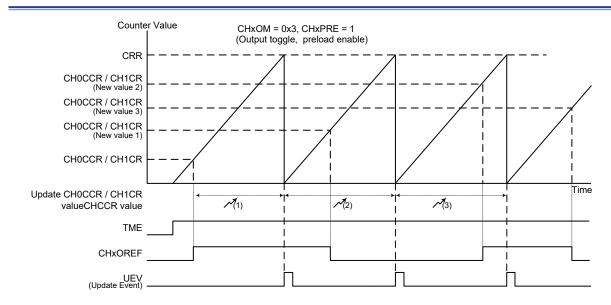

| Counter Mode                                      |     |

| Clock Controller                                  |     |

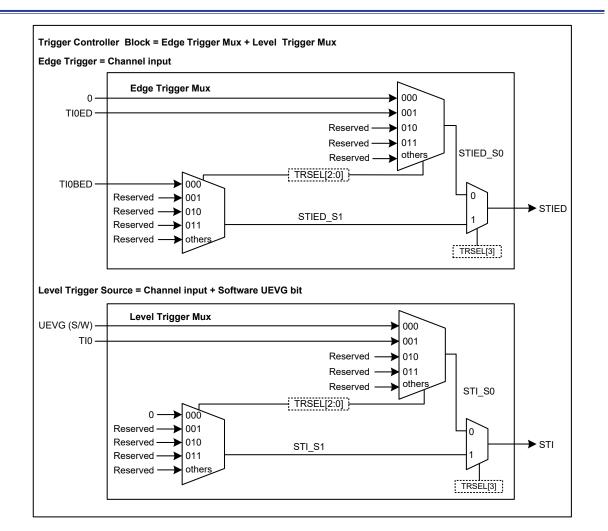

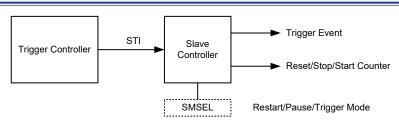

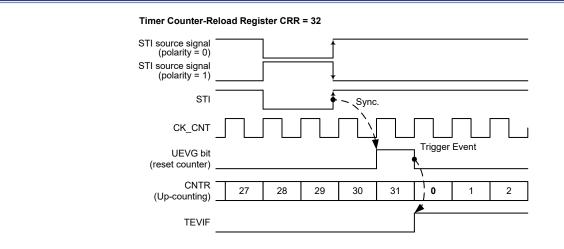

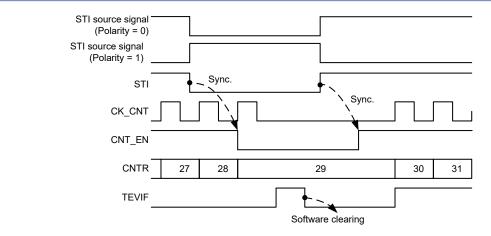

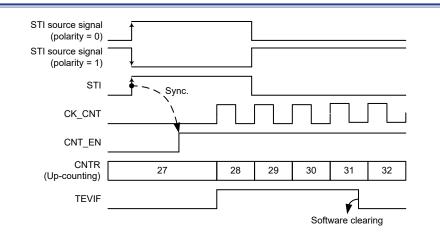

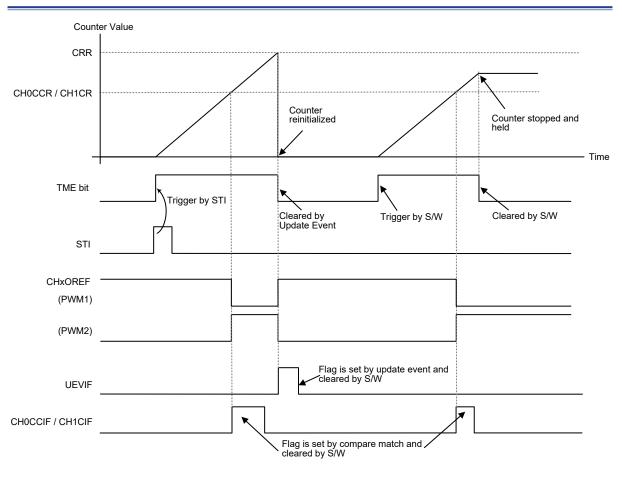

| Trigger Controller                                |     |

| Slave Controller                                  |     |

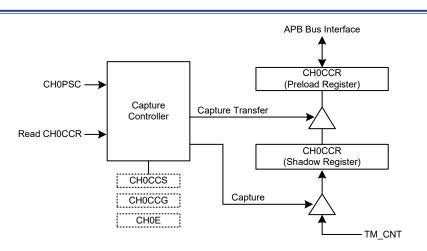

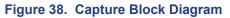

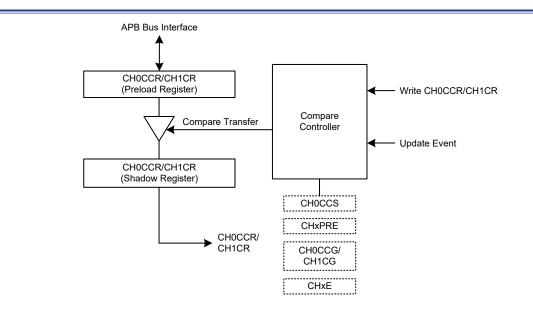

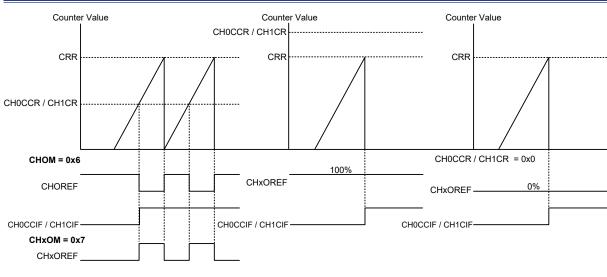

| Channel Controller                                |     |

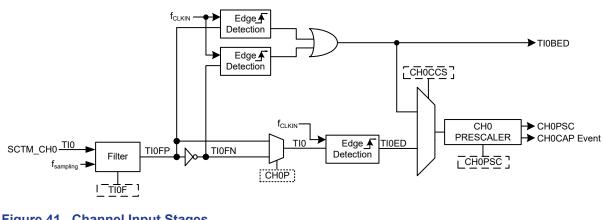

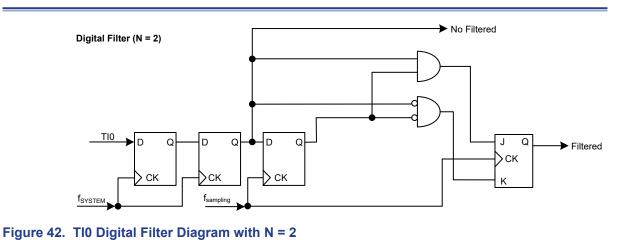

| Input Stage                                       |     |

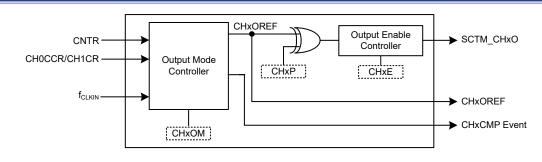

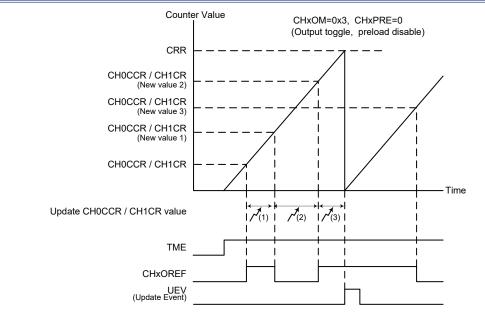

| Output Stage                                      |     |

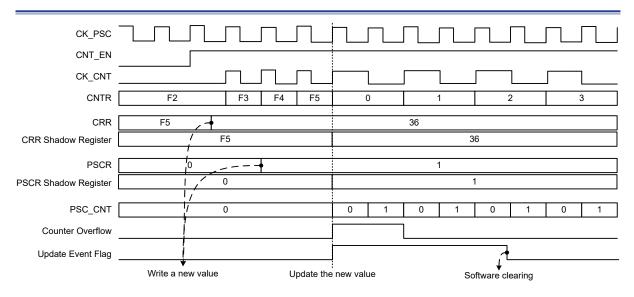

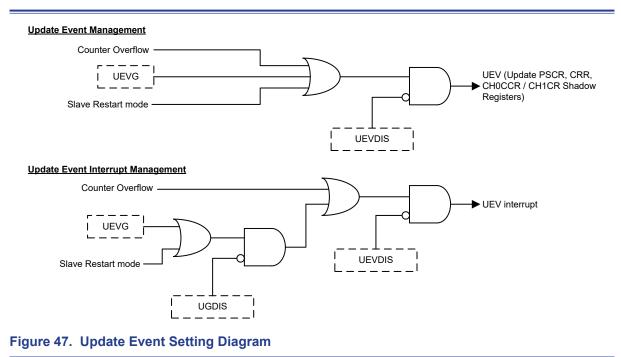

| Update Management                                 |     |

| Single Pulse Mode                                 |     |

| Register Map                                      |     |

| Register Descriptions                             |     |

| Timer Counter Configuration Register – CNTCFR     |     |

| Timer Mode Configuration Register – MDCFR         |     |

| Timer Trigger Configuration Register – TRCFR      |     |

| Timer Control Register – CTR                      |     |

| Channel 0 Input Configuration Register – CH0ICFR  |     |

| Channel 0 Output Configuration Register – CH0OCFR |     |

| Channel 1 Output Configuration Register – CH10CFR |     |

| Channel Control Register – CHCTR                  |     |

| Channel Polarity Configuration Register – CHPOLR  |     |

| Timer Interrupt Control Register – DICTR          |     |

| Timer Event Generator Register – EVGR             |     |

| Timer Interrupt Status Register – INTSR           |     |

| Timer Counter Register – CNTR                     |     |

| Timer Prescaler Register – PSCR                   |     |

| Timer Counter-Reload Register – CRR               |     |

| Channel 0 Capture/Compare Register – CH0CCR       |     |

| Channel 1 Compare Register – CH1CR                |     |

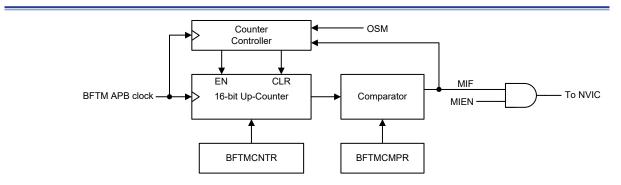

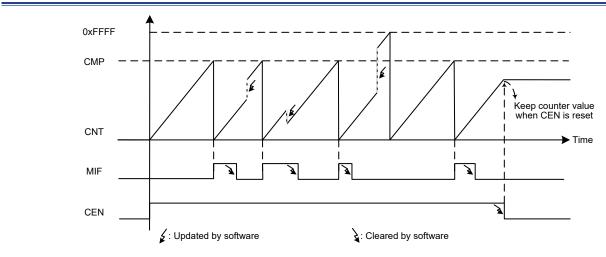

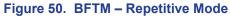

| 14 Basic Function Timer (BFTM)                    |     |

| Introduction                                      |     |

| Features                                          |     |

| Functional Description                            |     |

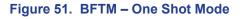

| Repetitive Mode                                   |     |

| One Shot Mode                                     |     |

| Register Map                                      |     |

| Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| BFTM Control Register – BFTMCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

| BFTM Status Register – BFTMSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

| BFTM Counter Value Register – BFTMCNTR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

| BFTM Compare Value Register – BFTMCMPR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

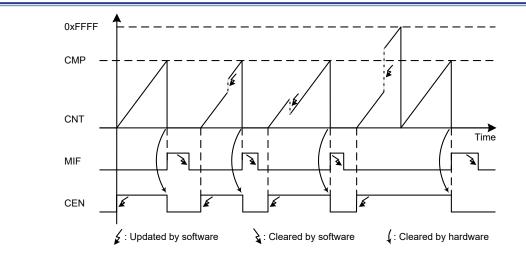

| 15 Real-Time Clock (RTC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

| Functional Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

| RTC Related Register Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

| Low Speed Clock Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

| RTC Counter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

| Interrupt and Wakeup Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| RTCOUT Output Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

| RTC Counter Register – RTCCNT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

| RTC Compare Register – RTCCMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

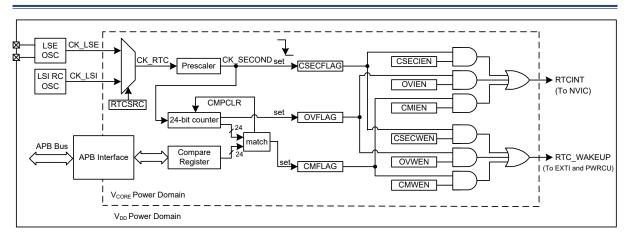

| RTC Control Register – RTCCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| RTC Status Register – RTCSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| RTC Interrupt and Wakeup Enable Register – RTCIWEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

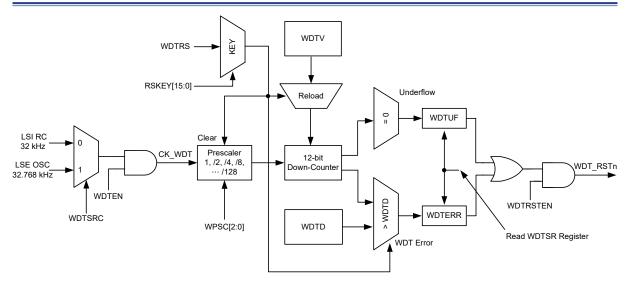

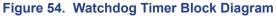

| 16 Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

| 16 Watchdog Timer (WDT)<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 214                                                                                                                                             |

| <b>16 Watchdog Timer (WDT)</b><br>Introduction<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 214<br>214                                                                                                                                      |

| 16 Watchdog Timer (WDT)<br>Introduction<br>Features.<br>Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 214<br>214<br>215                                                                                                                               |

| 16 Watchdog Timer (WDT)<br>Introduction<br>Features.<br>Functional Description<br>Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

| 16 Watchdog Timer (WDT)<br>Introduction<br>Features<br>Functional Description<br>Register Map<br>Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

| 16 Watchdog Timer (WDT)<br>Introduction<br>Features<br>Functional Description<br>Register Map<br>Register Descriptions.<br>Watchdog Timer Control Register – WDTCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

| <ul> <li>16 Watchdog Timer (WDT)</li> <li>Introduction</li> <li>Features</li> <li>Functional Description</li> <li>Register Map</li> <li>Register Descriptions</li> <li>Watchdog Timer Control Register – WDTCR</li> <li>Watchdog Timer Mode Register 0 – WDTMR0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

| <ul> <li>16 Watchdog Timer (WDT)</li> <li>Introduction</li> <li>Features</li> <li>Functional Description</li> <li>Register Map</li> <li>Register Descriptions</li> <li>Watchdog Timer Control Register – WDTCR</li> <li>Watchdog Timer Mode Register 0 – WDTMR0</li> <li>Watchdog Timer Mode Register 1 – WDTMR1</li> </ul>                                                                                                                                                                                                                                                                                                                                         | 214<br>214<br>215<br>215<br>216<br>217<br>217<br>217<br>218<br>219                                                                              |